# ELE336 Microprocessors Section 21 & 22 & 23

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

## Syllabus

Hacettepe University Department of Electrical and Electronics Engineering ELE 336 Microprocessor and Programming Spring All sections

Office Hours: TBD Email:

Prerequisite: This is a must course for regular students.

For others: In order to take this course you should have taken the prerequisite course ELE237 in the first semester of sophomore year and have done well. Here 'well' is very subjective so if you are not sure then you need to talk to me!.

#### TextBooks:

• M. A. Mazidi &. G. Mazidi,"The 80x86 IBM PC and Compatible Computers", Prentice Hall,2000 and above . <u>Supplemental Books:</u>

- Brey, The Intel Microprocessors, Prentice Hall, 5thEdition and above .

- Gaonkar, Microprocessor Architecture Programming and Apps /Prentice Hall. Besides the other aspects of the 8085 programming we will talk about the programmable 8085 peripherals and data transfer.

#### Useful Books:

Antonakos, An Introduction to the Intel Family of Microprocessors, Prentice Hall, 1999

K.R. Irvine, Assembly Language for Intel Based Computers, Prentice Hall, 1999.

W. A. Triebel and A. Singh, The 8088and 8086 Microprocessors: Programming, Interfacing, Software, Hardware and Applications" Prentice Hall, 2000

Flynn, Computer Architecture Pipelined and Parallel Processor Design

Computer Architecture and Logic Design, Thomas Bartee, McGraw Hill

and in combination with other computer architecture books available.

## Syllabus

LAB of the COURSE Essential Programs for the course: The DEBUG command on DOS(if you can find it). MASM Assembler, CODEVIEW and emu8086v103.zip. See lab web page (when available) for more information <u>Grading:</u> Midterm %40, Final %45,Homework %15

Attempts of cheating in Homeworks and Lab-Works will NOT be tolerated. No exceptions. <u>Attendance:</u> Required in ALL course hours and ALL LAB hours

# WEEKS

- 1. Introduction to Microcomputers and Microprocessors, 80x86 Processor Architecture

- 2. 80x86 Processor Architecture

- 3. 8088/8086 Instruction Set, Machine Codes, Addressing Modes, Debug

- 4. 8088/8086 Microprocessor Programming

- 5. 8088/8086 Microprocessor Programming

- 6. The 8088 and 8086 Microprocessors and Their Memory and Input/Output Interfaces, ISA Bus

- 7. Memory and Memory Interfacing

- 8. Input/Output Interface Circuits and Peripheral Devices 8255 MIDTERM WEEK

9. Midterm

10. Input/Output Interface Circuits and Peripheral Devices 8255

11. 8254 + Interrupt Interface of the 8088 and 8086 Microprocessors

12. Programmable Interrupt Controller (8259)

13. Serial Data Communication and 16450/8250/8251 chips

14. Co-processors and programming

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

#### Week 1

Introduction to Microcomputers and Microprocessors, Computer Codes, Programming, and Operating Systems

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

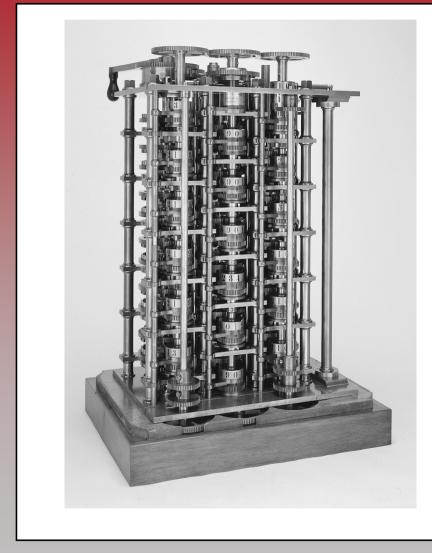

## First Computer

•It all started with the 1832 Babbage mechanical machine to calculate the navigation tables for the Royal Army, U.K.

The Babbage Difference Engine (1832)

**25,000 parts cost:** £17,470

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

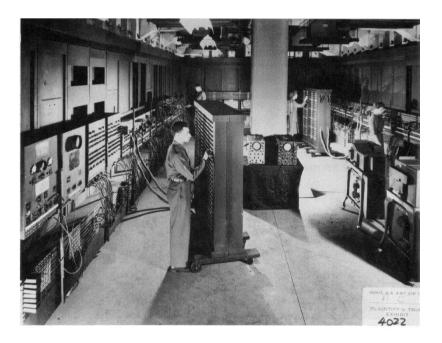

#### ENIAC

- Vacuum tube based

- "BIG BRAIN"

- ENIAC

- -1,800 sq. Feet area

- -30 ton

- 18000 vacuum tubes

- Application: IInd WW

1943 First electronic computer is used to decode the German Army secret codes, coded by the Enigma machine: Colossus, 1946 First General Purpose computer: ENIAC 17000 vacuum tubes, 500 miles of wire 30 tons, 100 000 ops per sec.@ U.of Penn

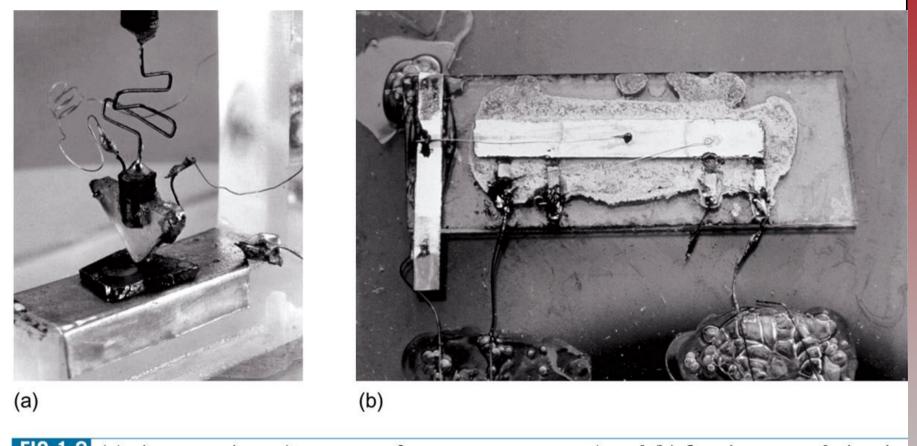

#### First Transistor

**FIG 1.2** (a) First transistor (Courtesy of Texas Instruments.) and (b) first integrated circuit. (Property of AT&T Archives. Reprinted with permission of AT&T.)

Bell Labs 1946

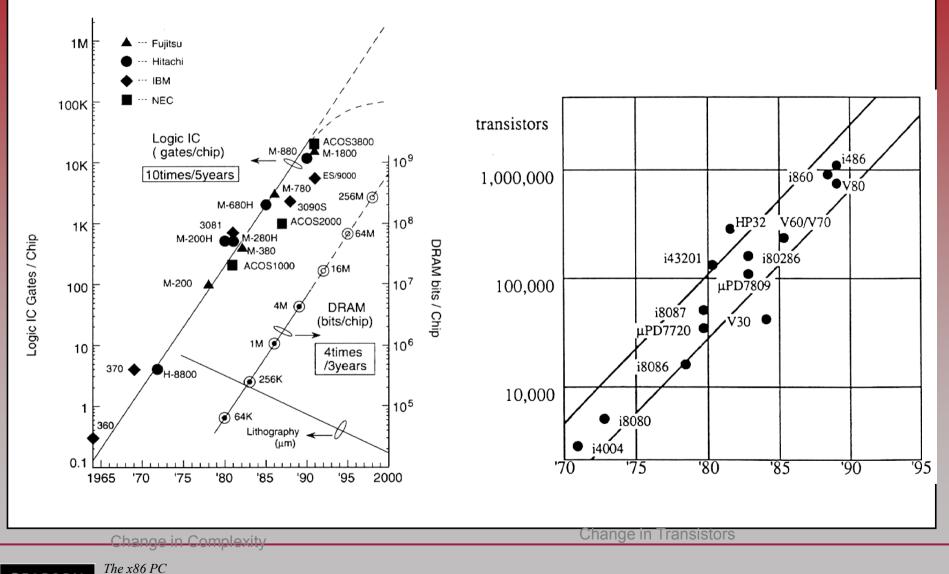

#### Change over the years

Assembly Language, Design, and Interfacing By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

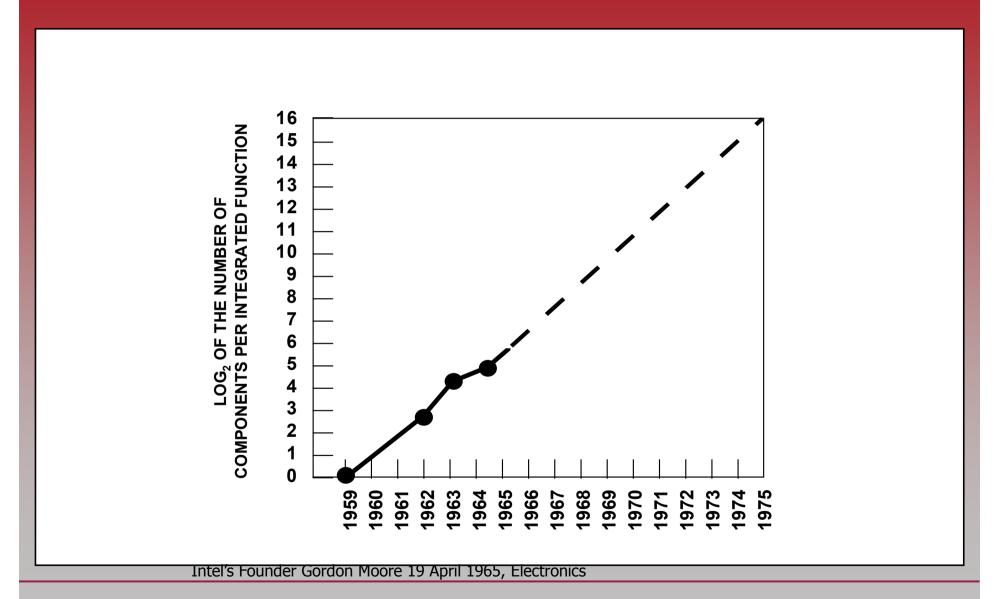

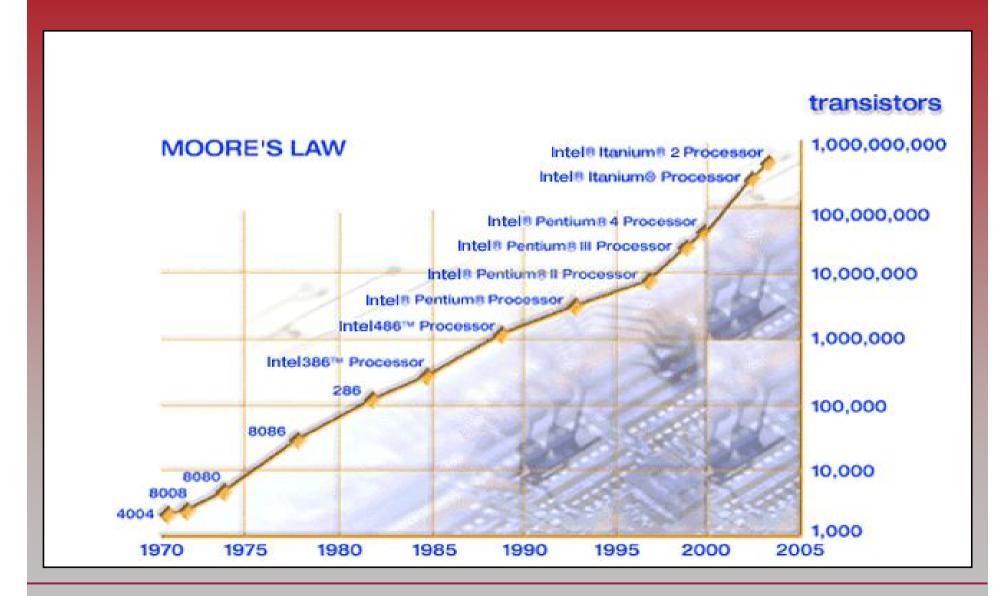

#### Moore's Law

PEARSON

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

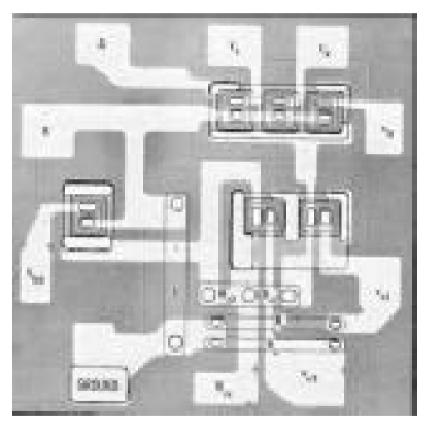

## First IC

<sup>•</sup>1958 Invention of the IC by Jack Kilby at Texas Instruments

Bipolar logic 1960's

ECL 3-input Gate Motorola 1966

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

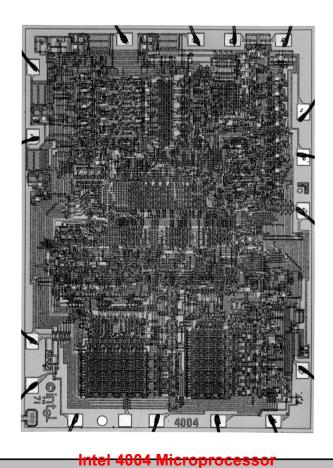

# A brief history

- First microprocessor at Intel in 1971--- 4004

- Intel 4004 was a 4 bit up. Only 45 instructions P Channel Mosfet technology. 50 K instructions per second (< ENIAC!).</li>

- Later 8008 as an 8 bit µ processor then 8080 and Motorolla 6800.

- 8080 was 10x faster than 8008 and TTL compatible (easy interfacing)

- MITS Altair 8800 1974. The BASIC Interpreter was written by Bill Gates. Assembler program was written by Digital Research Corporation (Author comp. Of Dr-DOS)

- 1977 8085 microprocessor. Internal clock generator, higher frequency at reduced cost and integration. There are 200 million 8085's around the world!

- 1978 8086+8088 microprocessors 16 bit. Addressed 1 Mbyte of memory. Small instruction cache (4-6 bytes) enabled prefetch of instructions.

- IBM decided to use 8088 in PC.

# A brief history

- In 1983 80286 released, identical to 8086 except the addressing and higher clock speed.

- 32 bit microprocessor era. In 1986 major overhaul on 80286 architecture → 80386 DX with 32bit data + 32 bit address (4 G bytes)

- 1989 80486 = 80386 +80387co processor + 8KB cache

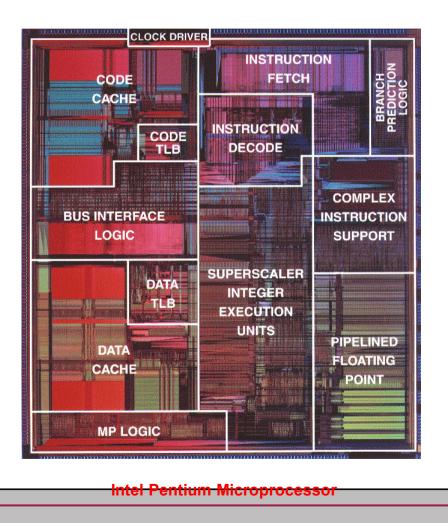

- 1993 Pentium (80586). Includes 2 execution engines.

- Pentium Pro included 256K Level 2 cache mechanism as well as Level 1 cache. Also 3 execution engines which can execute at the same time and can conflict and still execute in parallel. The address bus was expended to 36.

- Pentium 2 included L2 cache on its circuit board (called slot)

- Later Pentium 3 and 4 released with several architectural and technological innovations.

# Evolution of Intel Microprocessors

| Processor         | Codename | Year<br>Introduced | Transistors              | Minimum<br>Feature<br>Size<br>(microns) | Package                                             | Socket<br>or<br>Slot | Core/Bus<br>Frequency<br>(Max) <sup>1</sup> | External<br>Data<br>Bus<br>Width | Internal<br>Register<br>Widths | Address<br>Bus<br>Width | NDP <sup>2</sup> | L1<br>Cache                | L2<br>Cac  |

|-------------------|----------|--------------------|--------------------------|-----------------------------------------|-----------------------------------------------------|----------------------|---------------------------------------------|----------------------------------|--------------------------------|-------------------------|------------------|----------------------------|------------|

| 4004              |          | 1971               | 2,250                    | 10.0                                    | 16 pin DIP                                          |                      | .108 MHz                                    | 4                                | 8                              | 12                      | none             | none                       | not        |

| 8008              |          | 1972               | 3,500                    | 10.0                                    | 18 pin DIP                                          |                      | .200 MHz                                    | 8                                | 8                              | 14                      | none             | none                       | noi        |

| 8080              |          | 1974               | 6,000                    | 6.0                                     | 40 pin DIP                                          |                      | 3 MHz                                       | 8                                | 8                              | 16                      | none             | none                       | nor        |

| 8085 <sup>3</sup> |          | 1976               | 6,000                    | 6.0                                     | 40 pin DIP                                          |                      | 6 MHz                                       | 8                                | 8                              | 16                      | none             | none                       | noi        |

| 8086              |          | 1978               | 29,000                   | 3.0                                     | 40 pin DIP                                          |                      | 10 MHz                                      | 16                               | 16                             | 20                      | external         | none                       | noi        |

| 8088              |          | 1979               | 29,000                   | 3.0                                     | 40 pin DIP                                          |                      | 10 MHz                                      | 8                                | 16                             | 20                      | external         | none                       | noi        |

| 80286             |          | 1982               | 134,000                  | 1.5                                     | 68 pin<br>PLCC<br>or PGA⁴                           |                      | 12.5 MHz                                    | 16                               | 16                             | 24                      | external         | none                       | no         |

| 80386DX           |          | 1985               | 275,000                  | 1.0                                     | 132 pin<br>PGA<br>or QFP <sup>5</sup>               |                      | 33 MHz                                      | 32                               | 32                             | 32                      | external         | none                       | exter      |

| 80386SX           |          | 1988               | 275,000                  | 1.0                                     | 100 pin<br>PQFP <sup>7</sup>                        |                      | 33 MHz                                      | 16                               | 32                             | 24                      | external         | none                       | exte       |

| 80486DX           |          | 1989               | 1.2 million              | 0.8                                     | 168 pin<br>PGA                                      | Socket 3             | 50 MHz                                      | 32                               | 32                             | 32                      | on-chip          | 8 KB                       | exte:      |

| 80486SX           |          | 1991               | 1.185 million            | 1.0                                     | 196 lead<br>PQFP or<br>168 pin<br>PGA               | Socket 3             | 33 MHz                                      | 32                               | 32                             | 32                      | none             | 8 KB                       | exte       |

| 80486DX2          |          | 1992               | 1.2 million              | 0.6                                     | 168 pin<br>PGA                                      | Socket 3             | 66/33<br>MHz                                | 32                               | 32                             | 32                      | on-chip          | 8 KB                       | exte       |

| 80486DX4          |          | 1994               | 1.2 million              | 0.6                                     | 168 pin<br>PGA                                      | Socket 3             | 100/<br>33 MHz                              | 32                               | 32                             | 32                      | on-chip          | 8 KB                       | exte       |

| Pentium Classic   | P5       | 1993               | 3.1 million              | 0.8                                     | 273 pin<br>PGA                                      | Socket 4, 5          | 66 MHz                                      | 64                               | 32                             | 32                      | on-chip          | 8/8 KB<br>C/D <sup>8</sup> | exte       |

| Pentium Classic   | P54      | 1994               | 3.3 million              | 0.35,<br>0.5                            | 296 pin<br>PGA                                      | Socket 7             | 200/66<br>MHz                               | 64                               | 32                             | 32                      | on-chip          | 8/8 KB<br>C/D              | exte       |

| Pentium MMX       | P55      | 1997               | 4.5 million              | 0.25,<br>0.28                           | 296 pin<br>PGA                                      | Socket 7             | 300/66<br>MHz                               | 64                               | 32                             | 32                      | on-chip          | 16/16 KB<br>C/D            | exte       |

| Pentium Pro       | Р6       | 1995               | 5.5 million <sup>9</sup> | 0.35,<br>0.5                            | 387 pin dual<br>cavity PGA<br>or PPGA <sup>10</sup> | Socket 8             | 200/66<br>MHz                               | 64                               | 32                             | 36                      | on-chip          | 8/8 KB<br>C/D              | 256,<br>1M |

| Pentium II            | (Klamath)<br>Deschutes <sup>12</sup>   | (1997)<br>1998 | 7.5 million                               | (0.28),<br>(0.25) | 242 contact<br>SEC<br>cartridge                              | Slot 1     | (233/66<br>MHz)<br>450/100<br>MHz | 64  | 32 | 36 | on-chip | 16/16 KB<br>C/D | 512<br>KB <sup>13</sup>            |

|-----------------------|----------------------------------------|----------------|-------------------------------------------|-------------------|--------------------------------------------------------------|------------|-----------------------------------|-----|----|----|---------|-----------------|------------------------------------|

| Celeron               | (Covington)<br>Mendocino <sup>14</sup> | 1998           | (7.5 million)<br>19 million <sup>15</sup> | 0.25              | (242 contact<br>SEP<br>cartridge)                            | Slot 1     | (300/66<br>MHz)                   |     |    |    |         |                 |                                    |

|                       |                                        |                |                                           |                   | 370 pin<br>PPGA                                              | Socket 370 | 466/66<br>MHz                     | 64  | 32 | 36 | on-chip | 16/16<br>KB C/D | (external)<br>128 KB <sup>16</sup> |

| Pentium III           | Katmai                                 | 1999           | 9.5 million                               | 0.25              | 242 contact<br>SEC cartridge<br>330 contact<br>SEC cartridge | Slot 2     | 550/100<br>MHz                    | 64  | 32 | 36 | on-chip | 16/16 KB<br>C/D | 512 KB <sup>17</sup>               |

|                       | Coppermine                             | 1999           |                                           | 0.18              | 370 pin PGA                                                  |            | 733/133<br>MHz                    |     |    |    |         |                 | 256 KB <sup>18</sup>               |

| Itanium <sup>19</sup> | Merced                                 | 2000           |                                           | 0.18              |                                                              |            | 6XX/133                           | 128 | 64 | 64 | on-chip |                 | 256 KB <sup>20</sup>               |

MHz

<sup>1</sup>It is likely that higher frequency versions of the newer processors will be offered in the future.

<sup>2</sup>Numeric data processor (also called coprocessor or floating point unit).

<sup>3</sup>Improved 8080 with three new instructions to enable/disable three added interrupt pins. Simplified hardware with single +5 V power supply and on-board clock generator.

<sup>4</sup>Plastic leaded chip carrier or pin grid array.

<sup>5</sup>Quad flat package (OFP).

<sup>6</sup>Some 386 computers (and nearly all later processors) incorporated external L2 caches.

<sup>7</sup>Plastic quad flat package.

<sup>8</sup>Separate code and data caches are supplied

<sup>9</sup>On-board 256 KB L2 cache (separate silicon die) has 15.5 million transistors (31 million for 512 KB cache). 1 MB cache has two separate 512 KB die.

<sup>10</sup>Plastic pin grid array

<sup>11</sup>Separate die in package. Cache operates at core speed.

<sup>12</sup>Specifications for Klamath processor are shown in parentheses.

<sup>13</sup>Separate die in SEC package. Cache operates at one-half core speed.

<sup>14</sup>Specifications for the Covington processor are shown in parentheses. The Mendocino processor is also called Celeron A.

<sup>15</sup>Includes integrated 128 KB L2 cache.

<sup>16</sup>128 KB cache is on the same die with the processor and operates at the core frequency of the processor.

<sup>17</sup>Separate die operating at 0.5 times core speed (slot 1) or integrated with the processor operating at core speed (slot 2).

<sup>18</sup>Integrated with the processor and operating at core speed. Includes 256-bit (vs. 64 bit on previous chips) processor-cache data bus.

<sup>19</sup>Specifications for this processor have not yet been finalized by Intel.

<sup>20</sup>Integrated with the processor die and operating at full core speed.

## Old and New

The x86 PC

Assembly Language, Design, and Interfacing

By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

[Adapted from http://infopad.eecs.berkeley.edu/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign/2.cdesign

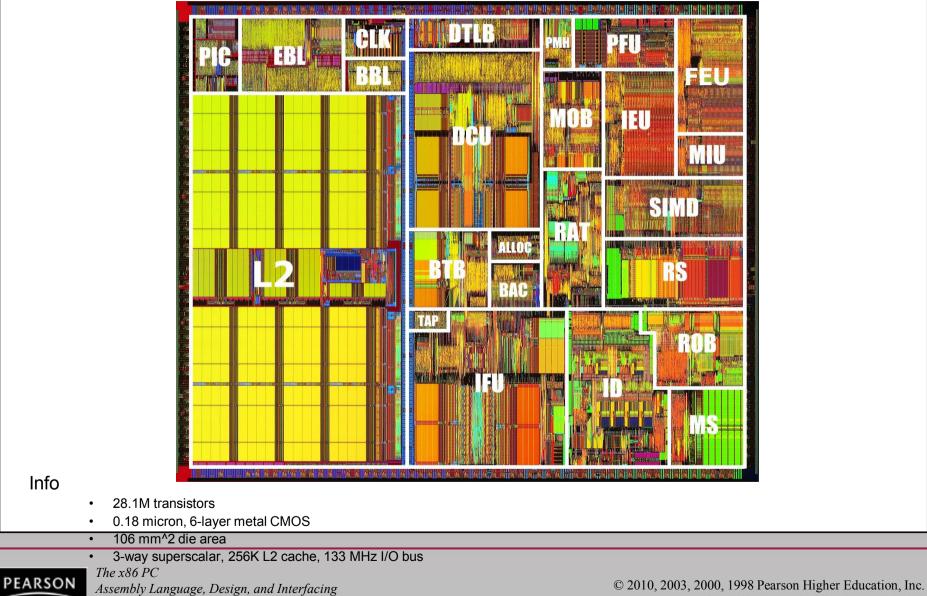

#### Pentium III

By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

#### Pentium IV

#### • 0.18-micron process technology (2, 1.9, 1.8, 1.7, 1.6, 1.5, and 1.4 GHz)

Introduction date: August 27, 2001

(2, 1.9 GHz); ...; November 20, 2000

(1.5, 1.4 GHz)

Level Two cache: 256 KB Advanced

Transfer Cache (Integrated)

- System Bus Speed: 400 MHz

- SSE2 SIMD Extensions

- Transistors: 42 Million

– Typical Use: Desktops and entrylevel workstations

- 0.13-micron process technology (2.53, 2.2, 2 GHz)

- Introduction date: January 7, 2002

- Level Two cache: 512 KB Advanced

- Transistors: 55 Million

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

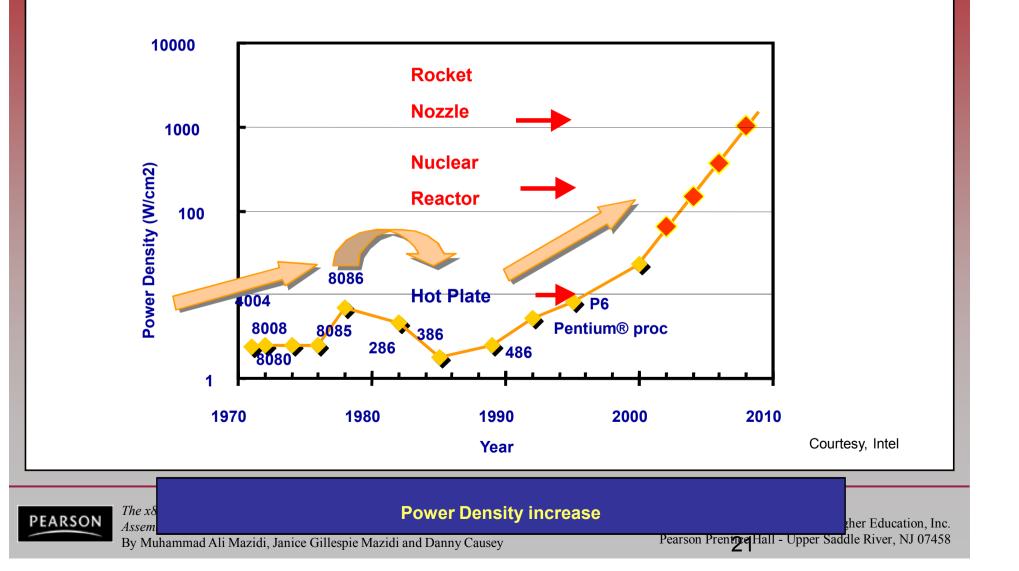

#### Change in Microprocessors

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

#### Power Density

#### Power Density

Assembly Language, Design, and Interfacing By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey 2010, 2005, 2000, 1990 Learson Englier Education, Inc. Pearson Prentige Hall - Upper Saddle River, NJ 07458

# Evolution in terms of Technology

| 10ai                                                                              | 1947 | 1950                              | 50 196                              | 51 196                                      | 66 197                             | 71 198                                   | 80 199                                                                            | 90 200                                                                     | )0          |

|-----------------------------------------------------------------------------------|------|-----------------------------------|-------------------------------------|---------------------------------------------|------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------|

| Technology                                                                        |      | Invention<br>of the<br>transistor | Discrete<br>components              | SSI                                         | MSI                                | LSI                                      | VLSI                                                                              | ULSI*                                                                      | GSI†        |

| Approximate<br>numbers of<br>transistors per<br>chip in<br>commercial<br>products |      | 1                                 | 1                                   | 10                                          | 100–1000                           | 1000–20,000                              | 20,000-<br>1,000,000                                                              | 1,000,000–<br>10,000,000                                                   | >10,000,000 |

| Typical<br>products                                                               |      |                                   | Junction<br>Transistor and<br>diode | Planar devices<br>Logic gates<br>Flip-flops | Counters<br>Multiplexers<br>Adders | 8 bit micro-<br>processors<br>ROM<br>RAM | 16 and 32<br>bit micro-<br>processors<br>Sophisticated<br>peripherals<br>GHM Dram | Special<br>processors,<br>Virtual<br>reality<br>machines,<br>smart sensors |             |

\* Ultra large-scale integration

† Giant-scale integration

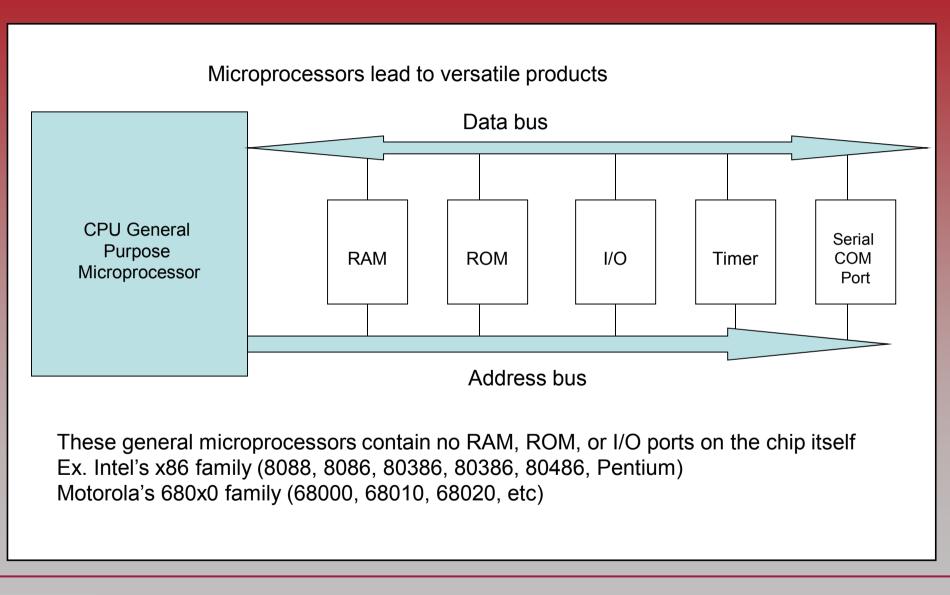

#### Types of Microcomputers

- *Microprocessor:* Processor on a chip

- In 1982, IBM began selling the idea of a *personal computer*. It featured a system board designed around the Intel 8088 8-bit microprocessor, 16 K memory and 5 expansion slots.

- This last feature was the most significant one as it opened the door for 3rd party vendors to supply video, printer, modem, disk drive, and RS 232 serial adapter cards.

- Generic PC: A computer with interchangable components manufactured by a variety of companies

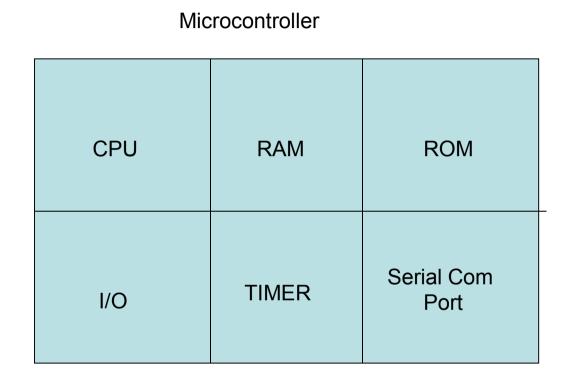

- Microcontroller is an entire computer on a chip, a microprocessor with onchip memory and I/O.

- These parts are designed into (embedded within) a product and run a program which never changes

- Home appliances, modern automobiles, heat, air-conditioning control, navigation systems

- Intel's MCS-51 family, for example, is based on an 8-bit microprocessor, but features up to 32K bytes of on-board ROM, 32 individually programmable digital input/output lines, a serial communications channel.

#### General Purpose Microprocessors

### Microcontrollers

A microcontroller has a CPU in addition to a fixed amount of RAM, ROM, I/O ports on one single chip; this makes them ideal for applications in which cost and space are critical Example: a TV remote control does not do computing power of a 486

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

#### Embedded Systems

- An embedded system uses a microcontroller or a microprocessor to do one task and one task only

- Example: toys, garage door openers, answering machines, ABS, keyless entry, etc.

- Inside every mouse, there is a microcontroller that performs the task of finding the mouse position and sends it to the PC

- Although microcontrollers are the preferred choice for embedded systems, there are times that the microcontroller is inadequate for the task

- Intel, Motorola, AMD, Cyrix have also targeted the embedded market with their general purpose microprocessors

- For example, Power PC microprocessors (IBM Motorola joint venture) are used in PCs and routers/switches today

- Microcontrollers differ in terms of their RAM, ROM, I/O sizes and type.

- ROM: One time-programmable, UV-ROM, flash memory

### Instruction Set

- The list of all recognizable instructions by the instruction decoder is called the instruction set

- CISC (Complex Instruction Set Computers), e.g., 80x86 family has more than 3000 instructions

- RISC (Reduced Instruction Set Computers) A small number of very fast executing instructions

- Most microprocessor chips today are allowed to fetch and execute cycles to overlap

- This is done by dividing the CPU into

- EU (Execution Unit)

- BIU (Bus Interface Unit)

- BIU fetches instructions from the memory as quickly as possible and stores them in a queue, EU then fetches the instructions from the queue not from the memory

- The total processing time is reduced

- Modern microprocessors also use a *pipelined* execution unit which allows the decoding and execution of instructions to be overlapped.

#### RISC versus CISC

#### Advantages of complex instruction set machines (CISC)

Less expensive due to the use of microcode; no need to hardwire a control unit Upwardly compatible because a new computer would contain a superset of the instructions of the earlier computers

Fewer instructions could be used to implement a given task, allowing for more efficient use of memory

Simplified compiler, because the microprogram instruction sets could be written to match the constructs of high-level languages

•More instructions can fit into the cache, since the instructions are not a fixed size

#### Disadvantages of CISC

Although the CISC philosophy did much to improve computer performance, it still had its drawbacks:

•Instruction sets and chip hardware became more complex with each generation of computers, since earlier generations of a processor family were contained as a subset in every new version

<sup>•</sup>Different instructions take different amount of time to execute due to their variable-length

Many instructions are not used frequently; Approximately 20% of the available instructions are used in a typical program

#### RISC versus CISC

#### Advantages of RISC

Advantages of a reduced instruction set machine:

Faster

Simple hardware

Shorter design cycle due to simpler hardware

#### Disadvantages of RISC

Drawbacks of a reduced instruction set computer include

•Programmer must pay close attention to instruction scheduling so that the processor does not spend a large amount of time waiting for an instruction to execute

<sup>•</sup>Debugging can be difficult due to the instruction scheduling Require very fast memory systems to feed them instructions

<sup>•</sup>Nearly all modern microprocessors, including the Pentium (hybrid RISC/CISC) Power PC, Alpha and SPARC microprocessors are superscalar

#### More on RISC and CISC

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

## Computer Operating Systems

• What happens when the computer is first turned on?

#### • MS-DOS

- A startup program in the BIOS is executed

- This program in turn accesses the master boot record on the floppy or hard disk drive

- A loader then transfers the system files IO.SYS and MSDOS.SYS from the disk drive to the main memory

- Finally, the command interpreter COMMAND.COM is loaded into memory which puts the DOS prompt on the screen that gives the user access to DOS's built-in commands like DIR, COPY, VER.

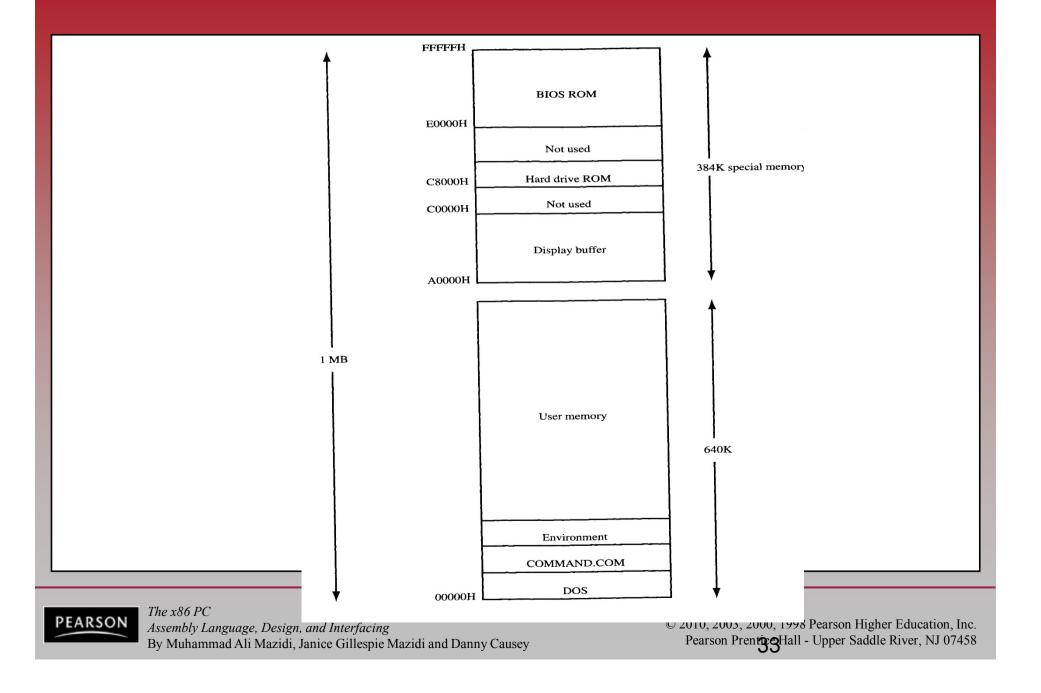

- The 640 K Barrier

- DOS was designed to run on the original IBM PC

- 8088 microprocessor, 1Mbytes of main memory

- IBM divided this 1Mb address space into specific blocks

- 640 K of RAM (user RAM)

- 384 K reserved for ROM functions (control programs for the video system, hard drive controller, and the basic input/output system)

#### Memory Map

## MS-DOS Functions and BIOS Services

- Program Support

- <u>BIOS</u>: usually stored in ROM these routines provide access to the hardware of the PC

- Access to the BIOS is done through the software interrupt instruction Int n

- For example, the BIOS keyboard services are accessed using the instruction INT 16h

- In addition to BIOS services DOS also provides higher level functions

- INT 21h

More details later

# 0.3 Inside the Computer terminology

• A bit is a binary digit that can have the value 0 or 1.

| Bit   |      |      |      | 0    |

|-------|------|------|------|------|

| Nibbl | e    |      |      | 0000 |

| Byte  |      |      | 0000 | 0000 |

| Word  | 0000 | 0000 | 0000 | 0000 |

- A *nibble* is 4 bits.

- A byte is defined as 8 bits.

- A word is two bytes, or 16 bits.

#### Some Important Terminology

- Bit is a binary digit that can have the value 0 or 1

- A byte is defines as 8 bits

- A nibble is half a byte

- A word is two bytes

- A double word is four bytes

- A kilobyte is 2^10 bytes (1024 bytes), The abbreviation K is most often used

- Example: A floppy disk holding 356Kbytes of data

- A megabyte or meg is 2^20 bytes, it is exactly 1,048,576 bytes

- A gigabyte is 2^30 bytes

# 0.3 Inside the Computer terminology

- A *kilobyte* is 2<sup>10</sup> bytes, which is 1,024 bytes.

- The abbreviation K is often used to represent kilobytes.

- A megabyte, or meg, is 2<sup>20</sup> bytes.

A little over 1 million bytes; exactly 1,048,576 bytes.

- A gigabyte is 2<sup>30</sup> bytes (over 1 billion).

- A *terabyte* is 2<sup>40</sup> bytes (over 1 trillion).

| Power of 2                |   |

|---------------------------|---|

| $2^{10} = 1024 = 1K$      |   |

| $2^{20} = 1024$ K = 1M    | 8 |

| $2^{30} = 1024M = 1G$     |   |

| $2^{40} = 1024$ G $= 1$ T |   |

#### 0.3 Inside the Computer two common memory types

- RAM which stands for "random access memory" (sometimes called *read/write memory*).

- Used for temporary storage of programs while running.

- Data is lost when the computer is turned off.

- RAM is sometimes called *volatile memory*.

- ROM stands for "read-only memory".

- Contains programs and information essential to the operation of the computer.

- Information in ROM is permanent, cannot be changed by the user, and is not lost when the power is turned off.

- ROM is called *nonvolatile memory*.

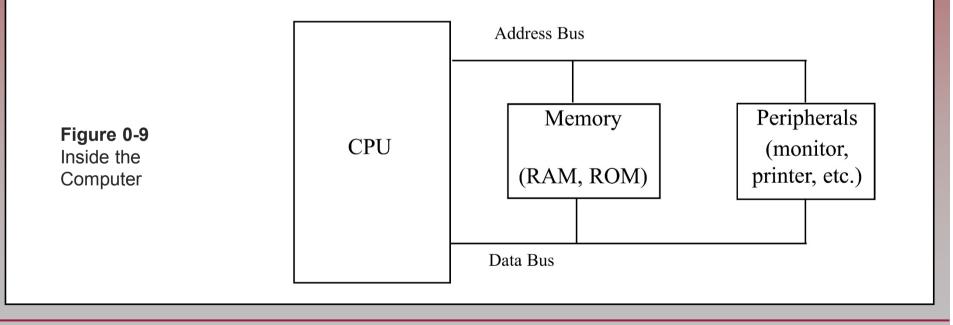

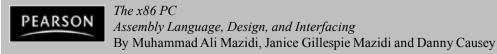

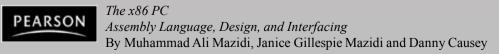

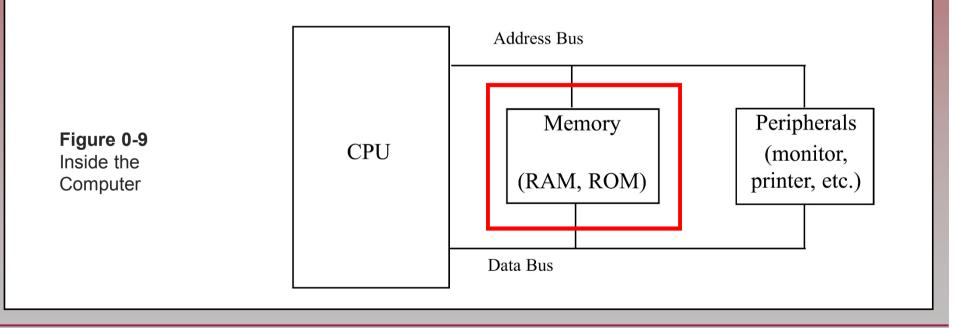

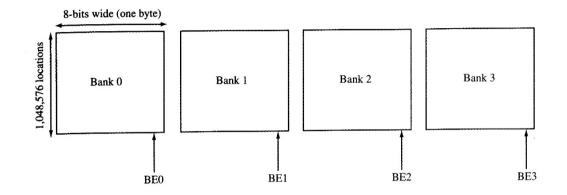

#### 0.3 Inside the Computer internal organization of computers

• Internal workings of every computer can be broken down into three parts:

# 0.3 Inside the Computer internal organization of computers

• Internal workings of every computer can be broken down into three parts:

- CPU (central processing unit).

#### 0.3 Inside the Computer internal organization of computers

- Internal workings of every computer can be broken down into three parts:

- CPU (central processing unit).

- Memory.

# 0.3 Inside the Computer internal organization of computers

- Internal workings of every computer can be broken down into three parts:

- CPU (central processing unit).

- Memory.

- I/O (input/output) devices.

# 0.3 Inside the Computer internal organization of computers

- CPU function is to execute (process) information stored in memory.

- I/O devices, such as keyboard & monitor provide a means of communicating with the CPU.

- The CPU is connected to memory and I/O through a group of wires called a *bus*.

- Allows signals to carry information from place to place.

In every computer there are three types of buses:

Address bus; Data bus; Control bus.

#### 0.3 Inside the Computer internal organization of computers

- For a device (memory or I/O) to be recognized by the CPU, it must be assigned an address.

- No two devices can have the same address.

- The address assigned to a given device must be unique.

- The CPU puts the address (in binary) on the address bus & decoding circuitry finds the device.

- The CPU then uses the data bus either to get data from that device or to send data to it.

- Control buses provide device read/write signals to indicate if the CPU is asking for, or sending information.

#### Three Bus System Architecture

- A collection of electronic signals all dedicated to particular task is called a *bus*

- data bus

- address bus

- control bus

- Data Bus

- The width of the data bus determines how much data the processor can read or write in one memory or I/O cycle (Machine Cycle)

- 8-bit microprocessor has an 8-bit data bus

- 80386SX 32-bit internal data bus, 16-bit external data bus

- 80386 32-bit internal and external data busses

- Data Buses are bidirectional.

- More data means more expensive computer however faster processing speed.

### 0.3 Inside the Computer more about the data bus

- As data buses carry information in/out of a CPU, the more data buses available, the better the CPU.

– More buses mean a more expensive CPU & computer.

- Data buses are bidirectional, because the CPU must use them either to receive or to send data.

– Average bus size is between 8 and 64.

- Computer processing power is related to bus size.

- An 8-bit bus can send out 1 byte a time.

- A 16-bit bus can send out 2 bytes at a time.

- Twice as fast.

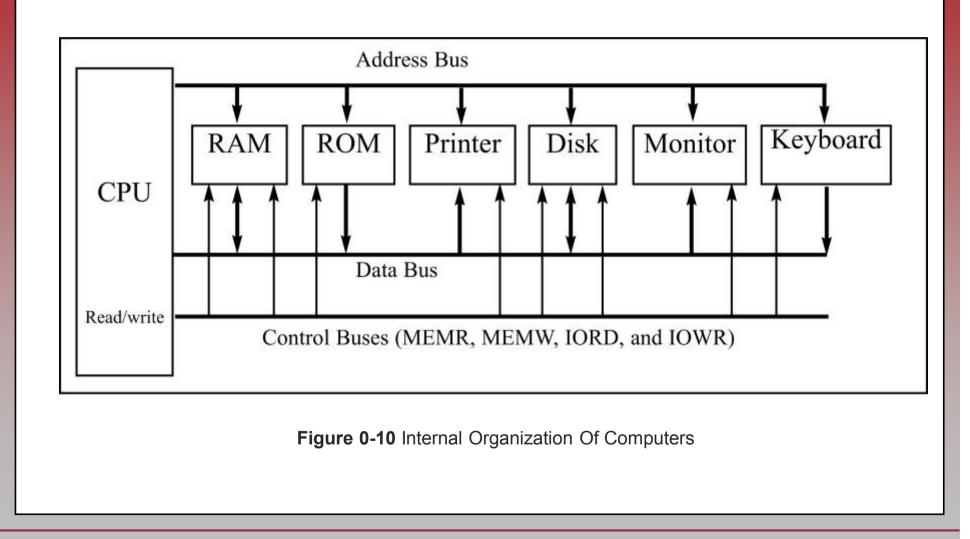

#### Address Bus

Here the Total amount of memory is 4Mbytes

- Address Bus Unidirectional

- The address bus is used to identify the memory location or I/O device (also called port) the processor intends to communicate with

- 20 bits for the 8086 and 8088

- 32 bits for the 80386/80486 and the Pentium

- 36 bits for the Pentium Pro

- 8086 has a 20-bit address bus and therefore addresses all combinations of addresses from all 0s to all 1s. This corresponds to 2<sup>20</sup> addresses or 1M (1 Meg) addresses or memory locations.

- Pentium: 4Gbyte main memory

### 0.3 Inside the Computer more about the address bus

- The address bus is used to identify devices and memory connected to the CPU.

- The more address bits available, the larger the number of devices that can be addressed.

- The number of CPU address bits determines the number of locations with which it can communicate.

- Always equal to 2<sup>x</sup>, where x is the number of address lines, regardless of the size of the data bus.

- The address bus is *unidirectional*.

- The CPU uses the bus only to send addresses out.

#### Control Bus

- Control bus is Uni-directional

- How can we tell the address is a memory address or an I/O port address

- Memory Read

- Memory Write

- I/O Read

- I/O Write

- When Memory Read or I/O Read are active, data is *input* to the processor.

- When Memory Write or I/O Write are active, data is *output* from the processor.

- The control bus signals are defined from the processor's point of view.

### 0.3 Inside the Computer internal organization of computers

*The x86 PC Assembly Language, Design, and Interfacing* By Muhammad Ali Mazidi, Janice Gillespie Mazidi and Danny Causey

#### 0.3 Inside the Computer CPU & relation to RAM and ROM

- For the CPU to process information, the data must be stored in RAM or ROM.

- The CPU cannot get the information from the disk directly because the disk is too slow.

- RAM & ROM are often referred to as *primary memory*.

- Disks are called *secondary memory*.

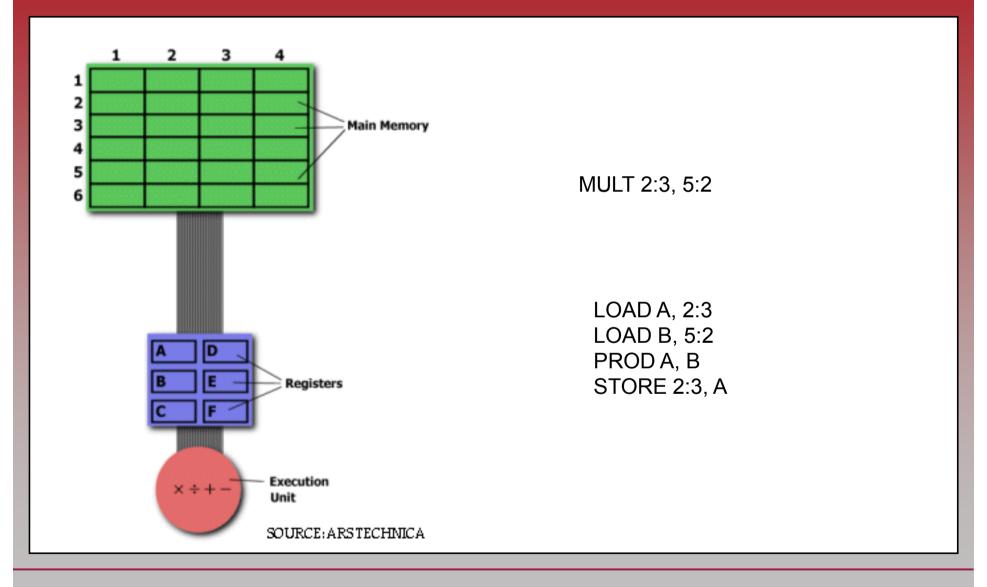

# 0.3 Inside the Computer inside CPUs

- A program stored in memory provides instructions to the CPU to perform an action.

- Adding payroll Address Bus numbers or Program Counter controlling Flags Instruction Register a robot. ALU Control Buses Instruction decoder, timing, and control Function of the CPU is to Data Bus Internal buses fetch these instructions Register A Register B from memory and then Register C execute them. Register D Figure 0-19 Internal Block Diagram of a CPU

#### 0.3 Inside the Computer CPU and relation to RAM and ROM

- To perform the actions of fetch and execute, all CPUs are equipped with resources such as...

- *Registers* to store information temporarily.

- 8, 16, 32, 64 bit, depending on CPU.

- ALU (arithmetic/logic unit) for arithmetic functions such as add, subtract, multiply, and divide.

- Also logic functions such as AND, OR, and NOT.

- *Program counter* to point to the address of the next instruction to be executed.

- In the IBM PC, a register called IP or instruction pointer.

- *Instruction decoder* to interpret the instruction fetched into the CPU.

- A step-by-step analysis of CPU processes to add three numbers, with steps & code shown.

- Assume a CPU has registers A, B, C, and D.

- An 8-bit data bus and a 16-bit address bus.

- The CPU can access memory addresses 0000 to FFFFH.

- A total of 10000H locations.

| Action                         | Code | Data |

|--------------------------------|------|------|

| Move value 21H into register A | BOH  | 21H  |

| Add value 42H to register A    | 04H  | 42H  |

| Add value 12H to register A    | 04H  | 12H  |

If the program to perform the actions listed above is stored in memory locations starting at 1400H, the following would represent the contents for each memory address location...

| Memory address | Contents of memory address                |

|----------------|-------------------------------------------|

| 1400           | (B0)code for moving a value to register A |

| 1401           | (21)value to be moved                     |

| 1402           | (04)code for adding a value to register A |

| 1403           | (42)value to be added                     |

| 1404           | (04)code for adding a value to register A |

| 1405           | (12)value to be added                     |

| 1406           | (F4)code for halt                         |

- The CPU's program counter can have a value between 0000 and FFFFH.

- The program counter must be set to the address of the first instruction code to be executed - 1400H.

| Memory address | Contents of memory address                |

|----------------|-------------------------------------------|

| 1400           | (B0)code for moving a value to register A |

| 1401           | (21)value to be moved                     |

| 1402           | (04)code for adding a value to register A |

| 1403           | (42)value to be added                     |

| 1404           | (04)code for adding a value to register A |

| 1405           | (12)value to be added                     |

| 1406           | (F4)code for halt                         |

- The CPU puts the address 1400H on the address bus and sends it out.

- Memory finds the location while the CPU activates the READ signal, indicating it wants the byte at 1400H.

- The content (B0) is put on the data bus & brought to the CPU.

| Memory address | Contents of memory address                |

|----------------|-------------------------------------------|

| 1400           | (B0)code for moving a value to register A |

| 1401           | (21)value to be moved                     |

| 1402           | (04)code for adding a value to register A |

| 1403           | (42)value to be added                     |

| 1404           | (04)code for adding a value to register A |

| 1405           | (12)value to be added                     |

| 1406           | (F4)code for halt                         |

- The CPU decodes the instruction B0 with the help of its instruction decoder dictionary.

- Bring the byte of the next memory location into CPU Register A.

| Memory address | Contents of memory address                |

|----------------|-------------------------------------------|

| 1400           | (B0)code for moving a value to register A |

| 1401           | (21)value to be moved                     |

| 1402           | (04)code for adding a value to register A |

| 1403           | (42)value to be added                     |

| 1404           | (04)code for adding a value to register A |

| 1405           | (12)value to be added                     |

| 1406           | (F4)code for halt                         |

- From memory location 1401H, the CPU fetches code 21H directly to Register A.

- After completing the instruction, the program counter points to the address of the next instruction - 1402H.

- Address 1402H is sent out on the address bus, to fetch the next instruction.

| Memory address | Contents of memory address                |

|----------------|-------------------------------------------|

| 1400           | (B0)code for moving a value to register A |

| 1401           | (21)value to be moved                     |

| 1402           | (04)code for adding a value to register A |

| 1403           | (42)value to be added                     |

| 1404           | (04)code for adding a value to register A |

| 1405           | (12)value to be added                     |

| 1406           | (F4)code for halt                         |

- From 1402H, the CPU fetches code 04H.

- After decoding, the CPU knows it must add the byte at the next address (1403) to the contents of register A.

- After it brings the value (42H) into the CPU, it provides the contents of Register A, along with this value to the ALU to perform the addition.

- Program counter becomes 1404, the next instruction address.

| Memory address | Contents of memory address                |

|----------------|-------------------------------------------|

| 1400           | (B0)code for moving a value to register A |

| 1401           | (21)value to be moved                     |

| 1402           | (04)code for adding a value to register A |

| 1403           | (42)value to be added                     |

| 1404           | (04)code for adding a value to register A |

| 1405           | (12)value to be added                     |

| 1406           | (F4)code for halt                         |

- Address 1404H is put on the address bus and the code is fetched, decoded, and executed.

- Again adding a value to Register A.

- The program counter is updated to 1406H

| Memory address | Contents of memory address                |

|----------------|-------------------------------------------|

| 1400           | (B0)code for moving a value to register A |

| 1401           | (21)value to be moved                     |

| 1402           | (04)code for adding a value to register A |

| 1403           | (42)value to be added                     |

| 1404           | (04)code for adding a value to register A |

| 1405           | (12)value to be added                     |

| 1406           | (F4)code for halt                         |

#### 0.4 Harvard and von Neumann CPU Architectures - internal workings

- The contents of address 1406 (HALT code) are fetched in and executed.

- The HALT instruction tells the CPU to stop incrementing the program counter and asking for the next instruction.

- Without HALT, the CPU would continue updating the program counter and fetching instructions.

| Contents of memory address                |

|-------------------------------------------|

| (B0)code for moving a value to register A |

| (21)value to be moved                     |

| (04)code for adding a value to register A |

| (42)value to be added                     |

| (04)code for adding a value to register A |

| (12)value to be added                     |

| (F4)code for halt                         |

|                                           |

### The x86 PC

assembly language, design, and interfacing fifth edition

MUHAMMAD ALI MAZIDI JANICE GILLISPIE MAZIDI DANNY CAUSEY