| AC-DC Load Lines of BJT Grcuits BJT AC Analysis                                                                                                                                                                                             |                     |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|

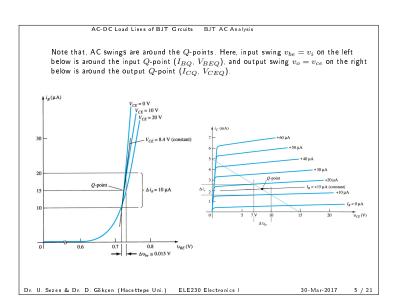

| BJT AC Analysis                                                                                                                                                                                                                             |                     |        |

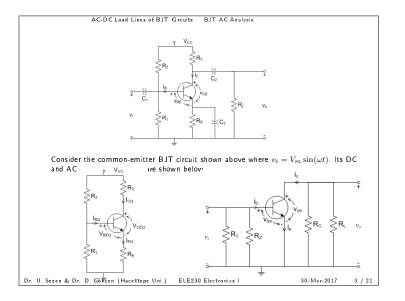

| <ol> <li>Draw the AC equivalent circuit (signal frequency is infinity, i.e.,<br/>a) Capacitors are short circuit, i.e., X<sub>C</sub> → 0.</li> <li>b) Kill the DC power sources (short-circuit DC voltage sourcurrent sources).</li> </ol> | ,                   | uit DC |

| <ol> <li>Write KVL for the loop which contains CE terminals</li> <li>a) Develop AC load-line equation.</li> </ol>                                                                                                                           |                     |        |

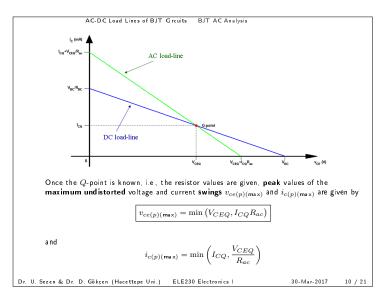

| 3. Draw AC-DC load lines                                                                                                                                                                                                                    |                     |        |

| a) Find available swings for a given input or find maximum                                                                                                                                                                                  | undistorted swings. |        |

|                                                                                                                                                                                                                                             |                     |        |

|                                                                                                                                                                                                                                             |                     |        |

|                                                                                                                                                                                                                                             |                     |        |

|                                                                                                                                                                                                                                             |                     |        |

|                                                                                                                                                                                                                                             |                     |        |

|                                                                                                                                                                                                                                             |                     |        |

| Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE230 Electronics I                                                                                                                                                                          | 30-Mar-2017         | 2 / 21 |

AC-DC Load Lines of BJT Grcuits BJT AC Analysis

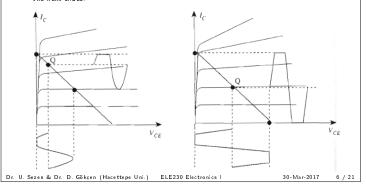

## Distortion

If the *Q*-point is incorrect as shown on the left below, or if the input is too high as shown on the right below, then the output swings (for a sinusoidal input) as shown in the figures below will be **distorted**, i.e., not the same shape as the input waveform. NOTE: Load-lines shown in the figures below are the AC load-lines which we will derive in the next slides.

## **Other Amplifier Configurations**

We developed and plotted AC-DC load lines for the common-emitter configuration. Now, let us look at other configurations.

- Common-base (CB) configuration

1. Obtain R<sub>ac</sub> from the CB loop.

2. Obtain R<sub>DC</sub> from the CE loop.

3. Draw the AC-DC load lines i<sub>C</sub> vs. v<sub>CE</sub> as before.

NOTE: You can also draw the AC-DC load lines as i<sub>C</sub> vs. v<sub>CB</sub> by shifting the

- voltage axis by  $V_{BE(ON)}$  volts to the left as  $V_{CBQ} = V_{CEQ} V_{BE(ON)}$ . Thus, current axis will be drawn at  $V_{CB(sat)} = V_{CE(sat)} V_{BE(ON)} = 0 V_{BE(ON)} = -V_{BE(ON)}$  volts not at 0V.

- Common-collector (CC) configuration (also known as emitter-follower)

- Common-collector (CC) configuration (also known as emitter-to

Obtain R<sub>ac</sub> and R<sub>DC</sub> from the CE loop as before.

Draw the AC-DC load lines i<sub>E</sub> vs. v<sub>CE</sub>.

- NOTE: As  $i_E\cong i_C$  , it will be the same as drawing  $i_C$  vs.  $v_{CE}$  .

- For pnp transistors, we express the currents in the reverse direction (i.e., having positive current values) and reverse the polarity of the terminal voltages (i.e., having positive voltage values), and then draw the AC-DC load lines, e.g.,  $i_C$  vs.  $v_{EC}$ .

- Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE230 Electronics I

30-Mar-2017 13 / 2

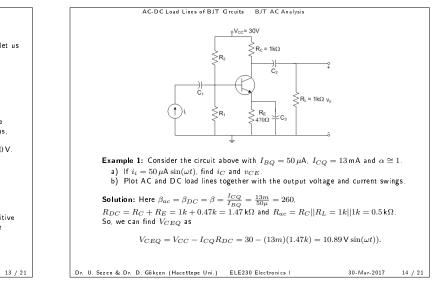

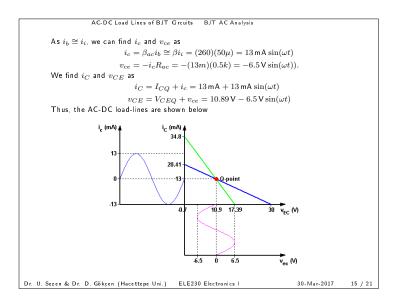

## AC-DC Load Lines of BJT Grcuits BJT AC Analysis

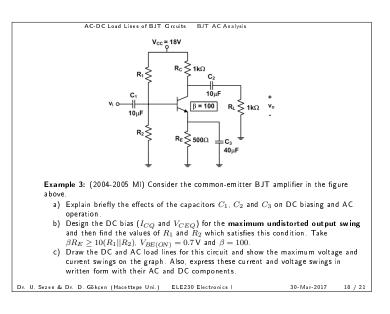

**Solution:** a. Capacitors are open-circuit in DC operation. Thus,  $C_1$  and  $C_2$  are called the coupling capacitors for the protection of the Q-point of the amplifier from the input and output circuitries by preventing the circulation/leakage of DC signals and enabling only AC signals in and out.  $C_3$  is called the emitter bypass capacitor ensuring the stability of the Q-point by enabling the emitter resistor to be in effect in DC operation and increasing the AC gain by bypassing the emitter resistor in AC operation.

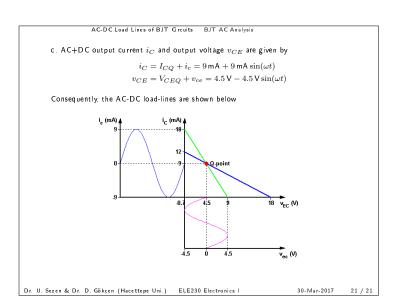

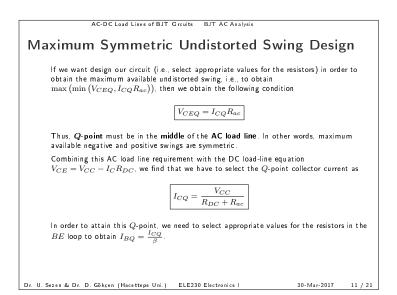

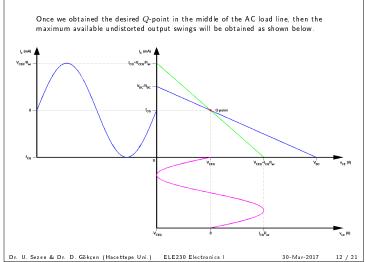

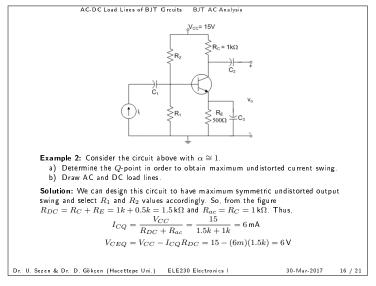

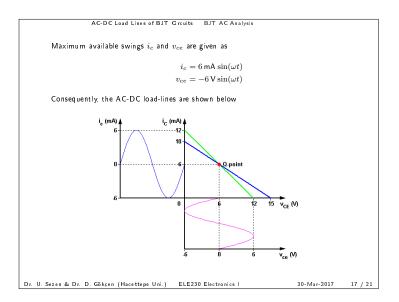

b. We can design this circuit to have maximum symmetric undistorted output swing and select  $R_1$  and  $R_2$  values accordingly. So, from the figure  $R_{DC}=R_C+R_E=1k+0.5k=1.5\,\mathrm{k\Omega}$  and  $R_{ac}=R_C||R_L=1k||1k=0.5\,\mathrm{k\Omega}.$  Thus,

$$\begin{split} I_{CQ} &= \frac{V_{CC}}{R_{DC}+R_{ac}} = \frac{18}{1.5k+0.5k} = 9 \text{ mA} \\ V_{CEQ} &= V_{CC} - I_{CQ}R_{DC} = 18 - (9m)(1.5k) = 4.5 \text{ V} \end{split}$$

As  $I_{EQ} \cong I_{CQ} = 9 \text{ mA}$ , base voltage  $V_{BQ}$  is given by

$V_{BQ} = V_{BE(ON)} + I_{EQ}R_E = 0.7 + (9m)(0.5k) = 5.2 \,\mathrm{V}.$

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE230 Electronics I

30-Mar-2017 19 / 21

By making the assumption  $\beta R_E \geq 10(R_1||R_2),$  we can ignore the base current  $I_{BQ}$  and directly apply the voltage divider rule as

$$\begin{split} \frac{R_2}{R_1+R_2} V_{CC} &\cong V_{BQ} \\ \frac{R_1+R_2}{R_2} &= \frac{V_{CC}}{V_{BQ}} \\ \frac{R_1}{R_2} &= \frac{V_{CC}}{V_{BQ}} - 1 = \frac{18}{5.2} - 1 = 2.46. \end{split}$$

Let us take the highest value of  $R_{BB}=R_1||R_2$  in order to reduce the currents through

$R_1$  and  $R_2$  as  $R_{BB}=R_1||R_2=\beta R_E/10=100*0.5/10=5\,\mathrm{k}\Omega$

If we take  $a=rac{R_1}{R_2}=2.46$ , then  $R_{BB}=rac{a}{a+1}R_2$ . So,  $R_2$  is given by

$$R_2 = \frac{a+1}{a}R_{BB} = \frac{2.46+1}{2.46}5k = 7.03\,\mathrm{kG}$$

Thus,  $R_1$  is given by

$$R_1 = aR_2 = (2.46)(7.03k) = 17.29\,\mathrm{k}\Omega$$

30-Mar-2017 20 / 21

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE230 Electronics I