#### Contents

RTL and DTL

Basic RTL Inverter

Basic RTL NOR and NAND Gates

Basic RTL Fan-Out

Basic RTL Power Dissipation

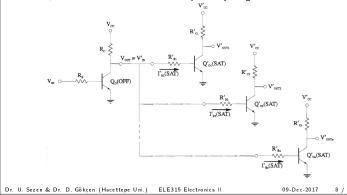

Basic RTL Non-Inverter

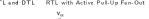

RTL with Active Pull-Up

RTL with Active Pull-Up Fan-Out

Basic DTL Inverter

Basic DTL NAND Gate

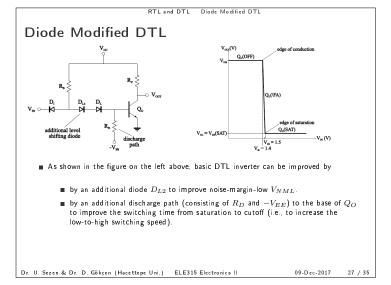

Diode Modified DTL

Transistor Modified DTL

DTL NAND Gate

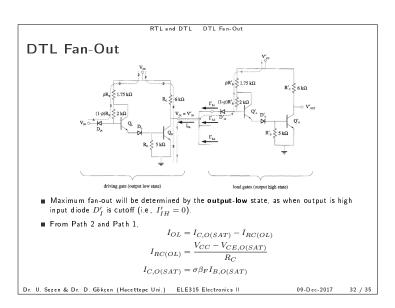

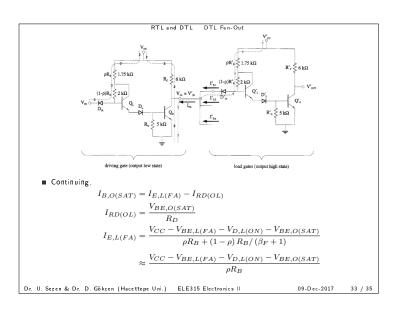

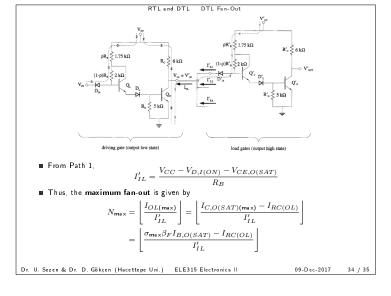

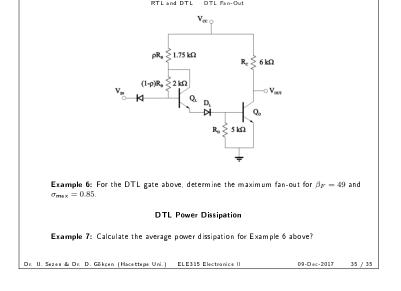

DTL Fan-Out

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017

RTL and DTL Basic RTL Inverter

# Resistor-Transistor Logic (RTL)

Resistor-Transistor Logic (RTL) which is introduced in 1962, is constructed from resistors and BJTs as shown in the figure on the left below

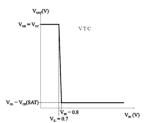

A basic RTL inverter and its VTC are shown in the figure on the left and right above, respectively

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017

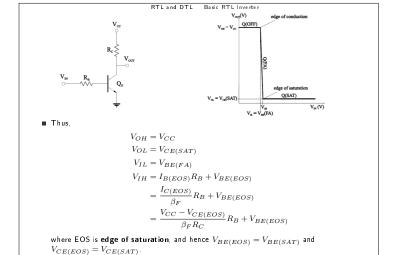

- lacksquare Here,  $Q_O$  is in cutoff (OFF) state when the input voltage is zero, i.e.,  $V_{IN}=0$ , consequently output is HIGH as  $V_{OUT} = V_{CC}$  (because  $I_{C} = 0$ )

- $\blacksquare$  When the input voltage is enough, i.e.,  $V_{IN}=V_{BE(FA)}$ , to turn on  $Q_O$  into the forward active (FA) mode, then current  $I_C$  will start to flow

- $\blacksquare$  Hence,  $V_{OUT}$  starts to drop with increasing  $V_{IN}$  as  $V_{OUT}=V_{CC}-I_CR_C,~I_C=\beta_FI_B$  and  $I_B=\frac{V_{IN}-V_{BE,O(FA)}}{V_{IN}-V_{BE,O(FA)}}$ .

- $\blacksquare$  If we increase  $V_{IN}$  further, at some point (i.e., when  $V_{IN}=V_{IH}$ )  $Q_O$  goes into saturation. Consequently, output becomes LOW and remains constant at  $V_{OUT} = V_{CE(SAT)}$

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017

09-Dec-2017

lacksquare We can summarize the state of the BJT transistor  $Q_O$  for output-high and output-low states as indicated in the table below

#### State of Active Elements for Output-High and Output-Low States

RTL and DTL Basic RTL NOR and NAND Gates

| Element | $V_{OH}$     | $V_{OL}$        |

|---------|--------------|-----------------|

| $Q_O$   | Cutoff (OFF) | Saturated (SAT) |

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II 09-Dec-2017

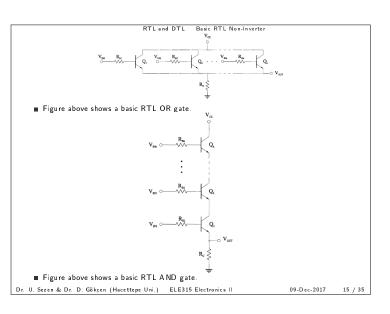

Basic RTL NOR and NAND Gates

■ Figure above shows a basic RTL NOR gate ■ Figure above shows a basic RTL NAND gate. Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) 09-Dec-2017 **Example 1:** For the basic RTL NA ND gate above, determine the maximum fan-in if all stack BJTs have  $V_{CE(SAT)}=0.17\,\mathrm{V}$  and all load gates have  $V_{BE(FA)}=0.7\,\mathrm{V}$ .

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017 7 / 3

RTL and DTL Basic RTL Fan-Out

## Basic RTL Fan-Out

- When a basic RTL inverter is in **output-low** state, any load gate would be in cutoff mode and draw no input current.

- Thus, maximum fan-out will be determined by the output-high state as shown below.

RTL and DTL Basic RTL Fan-Out

$$V_{\alpha}$$

$$V_{\alpha}$$

$$V_{\alpha} = V_{\alpha} = V_{\alpha}$$

$$V_{\alpha} = V_{\alpha}$$

$$V_{\alpha}$$

- $\blacksquare$  Output voltage is given by  $V_{OH}=V_{CC}-I_{OH}R_C$  where  $I_{OH}=I_{RC}$  and  $V_{OUT}=V_{OH}$ . So,  $V_{OH}$  is **not constant** and decreases with each added load gates, as the output current  $I_{OH}$  increases by each added load gate.

- $\blacksquare$  Thus, output current  $I_{OH}$  which is the sum of the identical input currents  $I'_{IH}$  of N load gates, is given by

$$I_{OH} = \frac{V_{CC} - V_{OH}}{R_C} = NI'_{IH}$$

where  $I_{IH}^{\prime}$  is given by

$$I'_{IH} = \frac{V_{OH} - V'_{BE(SAT)}}{R'_B}. \label{eq:IH}$$

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017

09-Dec-2017 11 / 35

9 / 35

$$\begin{array}{c} \text{RTL and DTL} \quad \text{Basic RTL Fan-Out} \\ V_{c} \\$$

■ Then, number of load gates, i.e., fan-out, (dropping the prime signs) is given by

$$N = \frac{V_{CC} - V_{OH}}{V_{OH} - V_{BE(SAT)}} \frac{R_B}{R_C}$$

■ Consequently, maximum fan-out is given by

$$N_{\mathsf{max}} = \left\lfloor \frac{V_{CC} - V_{OH(\mathsf{min})}}{V_{OH(\mathsf{min})} - V_{BE(SAT)}} \frac{R_B}{R_C} \right\rfloor$$

$\blacksquare \ \, \text{As} \, \, V_{OH(\min)} = V_{IH}.$

$$N_{\mathsf{max}} = \left\lfloor \frac{V_{CC} - V_{IH}}{V_{IH} - V_{BE(SAT)}} \frac{R_B}{R_C} \right\rfloor$$

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017 10 / 35

$V_{a} \circ \bigvee_{i} V_{i} \circ \bigvee_{i}$

**Example 2:** Determine the maximum fan-out for a basic RTL inverter with  $V_{CC}=5$  V,  $R_B=10$  k $\Omega$ ,  $R_C=1$  k $\Omega$ ,  $\beta_F=25$ ,  $V_{BE(SAT)}=0.8$  V and  $V_{CE(SAT)}=0.2$ V.

RTL and DTL Basic RTL Power Dissipation

## Basic RTL Power Dissipation

$\blacksquare$  As  $V_{OL}=V_{CE(SAT)}$  all load gates will be in cutoff mode. So, **output-low current supplied** is independent of load gates and given by

$$I_{CC(OL)} = \frac{V_{CC} - V_{CE,O(SAT)}}{R_C}$$

■ However, output-high current supplied depends on the number of load gates connected and given by  $VCC = V_{n, p, q, p, p, q}^{\prime}$

$$I_{CC(OH)} = \frac{V_{CC} - V_{BE(SAT)}'}{R_C + R'B/N} \label{eq:ccoh}$$

If there is no load,  $I_{CC(OH)}=0$ .

■ Consequently, average power dissipation is given by

$$P_{CC(\mathsf{avg})} = \frac{I_{CC(OL)} + I_{CC(OH)}}{2} \, V_{CC}$$

RTL and DTL Basic RTL Power Dissipation  $\begin{array}{c} v_{\alpha} \\ v_{\alpha}$

09-Dec-2017

13 / 35

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

Basic RTL Non-Inverter  $V_{oc}$   $V_{o$

where EOS is  ${\bf edge}$  of saturation, and hence  $V_{BC(EOS)}=V_{BC(SAT)}$  and  $V_{CE(EOS)}=V_{CE(SAT)}$  .

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II 0

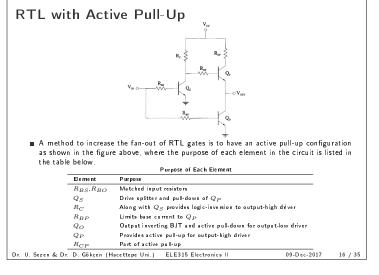

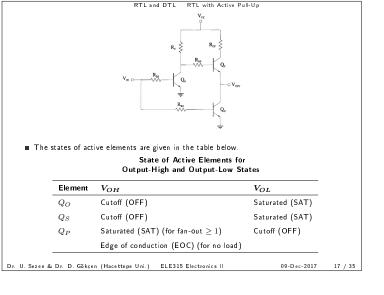

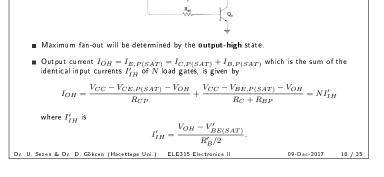

RTL and DTL RTL with Active Pull-Up

RTL and DTL RTL with Active Pull-Up Fan-Out

RTL with Active Pull-Up Fan-Out

■ Then, number of load gates, i.e., fan-out, (dropping the prime signs) is given by

$$N = \frac{V_{CC} - V_{CE(SAT)} - V_{OH}}{V_{OH} - V_{BE(SAT)}} \frac{R_B}{2R_{CP}} + \frac{V_{CC} - V_{BE(SAT)} - V_{OH}}{V_{OH} - V_{BE(SAT)}} \frac{R_B}{2\left(R_C + R_{BP}\right)}$$

$\blacksquare$  As  $V_{OH(\min)} = V_{IH}$  , maximum fan-out is given by

$$N_{\max} = \left\lfloor \frac{V_{CC} - V_{CE(SAT)} - V_{IH}}{V_{IH} - V_{BE(SAT)}} \frac{R_B}{2R_{CP}} + \frac{V_{CC} - V_{BE(SAT)} - V_{IH}}{V_{IH} - V_{BE(SAT)}} \frac{R_B}{2(R_C + R_{BP})} \right\rfloor$$

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017 1

$\blacksquare$  If we ignore  $I_{B,P(SAT)}$  (i.e.  $(R_C+R_{BP})\gg R_{CP})$  , maximum fan-out simplifies to

$$N_{\rm max} \approx \left\lfloor \frac{V_{CC} - V_{CE(SAT)} - V_{IH}}{V_{IH} - V_{BE(SAT)}} \frac{R_B}{2R_{CP}} \right\rfloor$$

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017 20 / 35

RTL and DTL RTL with Active Pull-Up Fan-Out

**Example 4:** Compare the maximum fan-out for the RTL inverter with active pull-up with that of basic RTL inverter where  $V_{CC}=5\,\mathrm{V},\,R_{BP}=R_{BS}=R_{BO}=10\,\mathrm{k}\Omega,\,R_{C}=1\,\mathrm{k}\Omega,\,R_{CP}=100\,\Omega,\,V_{BE(SAT)}=0.8\,\mathrm{V},\,V_{CE(SAT)}=0.2\,\mathrm{V}$  and  $\beta_F=25.$

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017 21 / 35

RTL and DTL Basic DTL Inverter

# Diode-Transistor Logic (DTL)

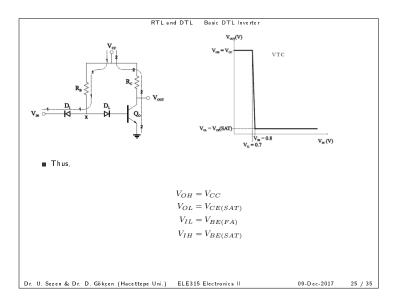

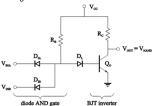

■ Diode-Transistor Logic (DTL) which is introduced in 1964 in order to overcome the low fan-out of RTL, is constructed from diodes and BJTs as shown in the figure on the left below.

A basic DTL inverter and its VTC are shown in the figure on the left and right above, respectively.

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017 22 / 35

$\begin{tabular}{ll} \hline \textbf{W} \begin{tabular}{ll} When the input is low, e.g., $V_{IN}=0$ V, input diode $D_I$ is forward biased so the voltage $V_x$ between the diodes will be $V_x=V_{IN}+V_{D,I(ON)}$ and thus as $V_{BE,O}=V_x-V_{D,L(ON)}=V_{IN}$, output transistor $Q_O$ will be in ${\bf cutoff}$ mode. Consequently, output is HIGH as $V_{OUT}=V_{CC}$ (because $I_C=0$) $ \end{tabular}$

$$V_x = V_{IN} + V_{D,I(ON)} \qquad \qquad \text{(while $V_{IN} < V_{BE(SAT)}$)}$$

$$V_{BE,O} = V_x - V_{D,L(ON)}$$

$$V_{BE,O} = V_{IN}$$

$\blacksquare$  When the input voltage is high enough, i.e.,  $V_{IN}=V_{BE(FA)}$ , to turn on  $Q_O$  into the forward active (FA) mode, then current  $I_C$  will start to flow.

■ Hence,  $V_{OUT}$  starts to drop with increasing  $V_{IN}$  as  $V_{OUT} = V_{CC} - I_C R_C$ .

$\blacksquare$  If we increase  $V_{IN}$  further, at some point (i.e., when  $V_{IN}=V_{BE(SAT)}$ ),  $Q_O$  goes into saturation and  $D_I$  starts to turn off. As a result,  $V_{OUT}$  becomes LOW and remains constant at  $V_{OUT}=V_{CE,O(SAT)}$ .

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

09-Dec-2017 23 / 35

RTL and DTL Basic DTL Inverter  $V_{oc} \\ V_{oc} \\ V_{w} = 0.7$

■ We can summarize the state of the active elements for output-high and output-low states as indicated in the table below.

#### State of Active Elements for Output-High and Output-Low States

| Element | $V_{OH}$                 | $V_{OL}$        |

|---------|--------------------------|-----------------|

| $Q_O$   | Cutoff (OFF)             | Saturated (SAT) |

| $D_L$   | Edge of Conduction (EOC) | Conducting (ON) |

| $D_I$   | Conducting (ON)          | Cutoff (OFF)    |

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II 09-Dec-2017

RTL and DTL Basic DTL NAND Gate

#### Basic DTL NAND Gate

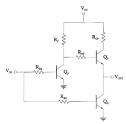

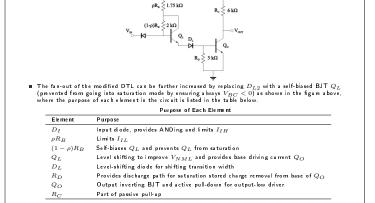

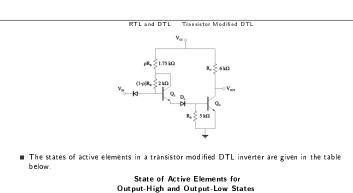

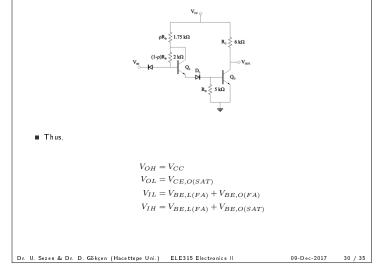

Transistor Modified DTL

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II

■ NAND function is inherently provided by the DTL logic family by adding diodes in parallel at the input pointing outward (i.e., towards the input) as shown in the figure below for a two-input basic DTL NAND gate.

Example 5: Consider the DTL NAND gate in the figure above, and determine

- a) Truth table for  $V_{INA},\ V_{INB}$  and  $V_{OUT}$  (using LOW-HIGH states),

- b) States of  $D_{IA}$ ,  $D_{IB}$  and  $Q_O$  when  $V_{INA}=0.4\,\mathrm{V}$  and  $V_{INB}=0.7\,\mathrm{V}$ ,

- c) States of  $D_{IA},\ D_{IB}$  and  $Q_O$  when  $V_{INA}=0.3\,\mathrm{V}$  and  $V_{INB}=0.4\,\mathrm{V},$

- d) States of  $D_{IA},~D_{IB}$  and  $Q_O$  when  $V_{INA}=0.53\,\mathrm{V}$  and  $V_{INB}=0.55\,\mathrm{V}$  .

- Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II 09-Dec-2017

09-Dec-2017

RTL and DTL Transistor Modified DTL

| •       | Output-111gh and Output-Low States |                     |   |

|---------|------------------------------------|---------------------|---|

| Element | $V_{OH}$                           | $V_{OL}$            | _ |

| $Q_O$   | Cutoff (OFF)                       | Saturated (SAT)     | _ |

| $D_L$   | Cutoff (OFF)                       | Conducting (ON)     |   |

| $Q_L$   | Cutoff (OFF)                       | Forward Active (FA) |   |

| $D_I$   | Conducting (ON)                    | Cutoff (OFF)        |   |

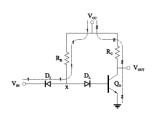

DTL NAND Gate

■ NAND function is inherently provided by the DTL logic family by adding diodes in parallel at the input pointing outward as shown in the figure below.

V<sub>ss</sub>

09-Dec-2017 31 / 35

Dr. U. Sezen & Dr. D. Gökçen (Hacettepe Uni.) ELE315 Electronics II